In today’s high-speed electronic systems, electromagnetic compatibility challenges can make or break a product’s success. Studies show that over 50% of electronic products fail their initial EMC testing, leading to costly redesigns and delayed market launches.

However, achieving electromagnetic compatibility doesn’t have to be a matter of trial and error. Specifically designed PCB layout techniques and methodical design approaches can effectively minimise EMI issues from the start. This comprehensive guide examines proven strategies for EMI design and demonstrates how proper PCB layout practises ensure first-pass EMC compliance.

Understanding EMC Design Fundamentals

Electromagnetic compatibility represents the cornerstone of reliable electronic design, essentially determining how well devices operate in their intended environment without causing or experiencing interference. Understanding EMC fundamentals begins with recognising that every electronic device must both limit its electromagnetic emissions and maintain immunity to external interference sources.

Key principles of electromagnetic compatibility

The foundation of EMC design rests on three fundamental principles:

- Minimising electromagnetic interference generation at the source

- Preventing interference transmission through coupling paths

- Protecting sensitive circuits from external disturbances

Critical factors affecting EMC performance

Notably, several critical factors influence EMC performance in PCB design. The selection of components and their placement significantly impacts electromagnetic emissions, with surface mount components offering superior EMC performance compared to radial and axial leaded alternatives. Furthermore, proper decoupling capacitor implementation proves crucial, as these components should be placed as close as possible to each IC to effectively reduce switching noise propagation across the board.

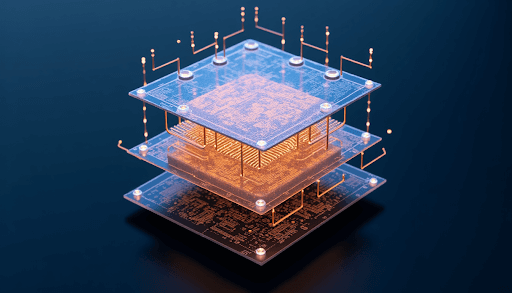

Impact of PCB layout on electromagnetic emissions

PCB layout fundamentally shapes electromagnetic emissions and system immunity. Studies indicate that boards designed without EMC considerations often fail initial compliance testing. Consequently, implementing proper layout techniques from the start becomes essential. The arrangement of ground planes, signal routing, and component placement directly influences the electromagnetic field containment.

A well-designed PCB layout incorporates strategic ground plane placement and maintains controlled impedance for high-speed signals. In essence, the layout must ensure that return currents follow their intended paths, as improper return paths can create unintended antennas that increase electromagnetic emissions.

Implementing Essential PCB Layout Techniques

Proper PCB layout serves as the foundation for achieving optimal electromagnetic compatibility in electronic designs. The implementation of essential layout techniques requires careful attention to component placement, ground plane design, and power distribution strategies.

Optimal component placement strategies

Board segregation plays a vital role in minimising electromagnetic interference. The layout should be divided into distinct sections based on circuit functionality:

- Digital circuits positioned away from sensitive components

- Input/output sections placed on one edge of the board

- Power supply components grouped in dedicated zones

- Analogue circuits isolated from high-frequency elements

Ground plane design and implementation

A well-designed ground plane forms the cornerstone of EMC-compliant PCB design. Studies indicate that maximising the ground area on a PCB notably reduces ground inductance, thereby minimising electromagnetic emissions and crosstalk. Moreover, implementing a solid, unbroken ground layer provides the least impedance value for signal returns.

Power distribution network optimisation

The Power Distribution Network (PDN) demands meticulous attention to ensure stable power delivery across the board. Particularly, the strategic placement of decoupling capacitors proves crucial – they should be positioned as close as possible to IC power pins to minimise current loops. Additionally, utilising multiple decoupling capacitors with varying capacitance values addresses a broader frequency range of noise.

For optimal PDN performance, trace routing requires careful consideration. Power and ground traces should run parallel when a separate power plane isn’t feasible. The implementation of wide trace widths with low-resistivity materials enables enhanced current flow, while multiple power planes result in reduced impedance paths.

Mastering Signal Routing for EMC

Signal routing represents a critical aspect of electromagnetic compatibility design, demanding careful attention to both trace layout and signal integrity. Indeed, proper routing techniques can significantly reduce electromagnetic interference while ensuring reliable signal transmission.

High-speed signal routing guidelines

Successful high-speed signal routing begins with minimising trace lengths and controlling impedance. According to industry standards, high-speed traces should maintain a separation of at least 2 times the trace width to reduce crosstalk. For optimal performance, consider these essential guidelines:

- Minimise signal trace lengths to reduce propagation delay

- Route traces over continuous ground planes

- Avoid 90-degree corners in favour of 45-degree turns

- Maintain consistent trace widths throughout the signal path

Differential pair routing techniques

Differential pair routing offers superior noise immunity and enhanced signal integrity. Important to realise, differential pairs should be routed as close together as possible to achieve optimal coupling. The traces in differential pairs must maintain equal lengths to ensure proper signal timing, with high-speed USB requiring length mismatches no greater than 150 mils.

Return path considerations

In light of EMC requirements, return path design proves crucial for minimising electromagnetic emissions. The return current always follows the path of least impedance, accordingly, providing a clear return path directly underneath signal traces becomes essential. At higher frequencies, the reactive component becomes more significant than resistance, making the loop inductance a critical factor.

The design must ensure continuous return paths, especially when signals transition between layers. For optimal performance, ground vias should be placed close to signal vias, reducing impedance discontinuities and minimising reflections. Furthermore, any slots or gaps in the ground plane should be avoided as they can create unintended antennas and increase emissions.

Applying Advanced EMC Design Strategies

Advanced electromagnetic compatibility strategies elevate PCB design beyond basic layout techniques, focusing on sophisticated methods to achieve optimal EMI performance. Proper implementation of these strategies often determines whether a board passes EMC testing on the first attempt.

Shielding and filtering techniques

Physical shielding serves as a crucial defence against electromagnetic interference. For optimal results, consider these proven shielding methods:

- Metal enclosures acting as Faraday cages for external EMI protection

- Cable shielding for high-speed signal protection

- Ferrite beads and chokes for high-frequency noise suppression

- Edge plating and conformal coatings for board-level protection

Stackup optimisation methods

Stackup configuration fundamentally influences EMC performance through proper layer arrangement and impedance control. A well-designed stackup minimises electromagnetic interference by optimising signal and return planes. Subsequently, maintaining controlled impedance becomes vital, notably for high-frequency signals where proper impedance control ensures signal integrity and minimal distortion.

Furthermore, sequential layer alignment proves essential, with high-speed signal layers strategically positioned below power planes to promote tight coupling and reduce electromagnetic interference. This arrangement effectively creates a shield against radiation from high-speed signals.

Decoupling and bypass techniques

Decoupling and bypass capacitors play distinct yet complementary roles in maintaining power integrity. Bypass capacitors should be positioned between an IC’s power supply pin and ground, therefore addressing voltage fluctuations specifically between the output pin and PCB ground plane.

Notably, for optimal performance:

- Place bypass capacitors as close as possible to power and ground pins

- Connect capacitors directly to ground/power planes through vias

- Use multiple capacitors with different values to target various noise frequencies

The implementation of these advanced strategies requires careful attention to detail and thorough understanding of electromagnetic principles. Through proper execution, these techniques effectively minimise EMI issues while ensuring robust circuit performance.

Conclusion

Electromagnetic compatibility challenges need not derail electronic product development. Though studies show many products fail initial EMC testing, proper implementation of proven PCB design techniques significantly increases first-pass success rates.

Strategic component placement, thoughtful ground plane design, and careful signal routing form the foundation of EMC-compliant boards. These fundamentals, combined with advanced strategies like optimal stackup configuration and proper shielding, create robust designs that minimise electromagnetic interference.

Success lies in addressing EMC requirements early during the PCB design phase. Rather than treating electromagnetic compatibility as an afterthought, designers who embrace these proven techniques from the start save considerable time and resources. Most importantly, they deliver reliable products that perform as intended in real-world environments.

References

- https://www.rocket-pcb.com/ensuring-emi-emc-compliance-in-industrial-pcbs-what-are-the-key-design-considerations-for-electromagnetic-compatibility

- https://runtimerec.com/designing-for-emi-emc-compliance/

- https://www.researchgate.net/publication/4240961_Impact_of_PCB_layout_design_on_final_product’s_EMI_compliance

- https://www.fresuelectronics.com/post/fundamentals-of-pcb-design-for-emc-emi

- https://www.academyofemc.com/emc-design-guidelines

- https://resources.altium.com/p/component-placement-for-emc

- https://www.raypcb.com/pcb-design-guidelines-for-emi-emc/

- https://www.protoexpress.com/blog/7-pcb-design-tips-solve-emi-emc-issues/

- https://www.tessolve.com/blogs/power-distribution-network-in-pcb-design-ensuring-stable-power-delivery/

- https://www.linkedin.com/pulse/optimising-power-distribution-networks-pcbs-electronics-%E9%A2%96-%E8%A2%81-zqzpch

- https://learnemc.com/pcb-layouth

- https://www.altium.com/documentation/altium-designer/interactively-routing-differential-pairs-pcb?srsltid=AfmBOoq63PUhX-9qXZWKqcb55PVy0_7re4vtVRPpGLMC6hbnrcomRNz

- https://semiengineering.com/pcb-design-rules-for-electromagnetic-compatibility/

- https://resources.altium.com/p/emi-shielding-techniques

- https://www.compeng.com.au/pcb-design-guidelines-tips-for-emi-and-emc/

- https://rushpcb.com/pcb-design-strategies-for-emi-emc-compliance/

- https://hilelectronic.com/pcb-stackup-guide/

- https://resources.altium.com/p/bypass-and-decoupling-capacitor-placement-guidelines